More and more companies are captivated by the RISC-V revolution (Reduced Instruction Set Computer - Version Five, say “risc-five”). With a golden future on the horizon, RISC-V is poised to reshape the computing landscape. Tech giants like Google are recognizing its potential, going so far as starting to make RISC-V a “tier-1 platform” in Android. The open-source nature of RISC-V invites collaboration and empowers developers to shape the future of computing. But what exactly is RISC-V, and what advantages does it hold in comparison to ARM and x86? In this article, we will embark on an enlightening journey to unravel the mysteries of RISC-V and delve into its extraordinary advantages.

What is an ISA?

Every CPU has the capability to manipulate data by moving bits and bytes from one memory address to the other and perform arithmetic operations like addition and multiplication. RISC-V, like any other Instruction Set Architecture (ISA), provides a specific set of instructions for CPUs to carry out these tasks, allowing programmers to create algorithms as a sequence of instructions. To simplify programming, high-level-languages like C/C++, Java or Python come into play, enabling developers to work with abstract concepts without needing to remember the exact memory addresses where values are stored. This necessitates the use of a compiler to translate high-level code into executable instructions for the ISA.

What is RISC-V?

RISC-V, an open-source ISA, originated from the research conducted at the University of California, Berkeley, starting in 2010. The project aimed to develop a new ISA that could address the shortcomings of existing architectures while promoting transparency and collaboration. As a result RISC-V was born, designed with simplicity and modularity in mind. Over the years, RISC-V gained momentum and attracted a growing community of developers and companies interested in its open nature and potential advantages.

Who uses RISC-V?

The disruptive potential of RISC-V has been capturing the attention of tech giants and innovative companies, with Google being just one of them. Alibaba, a major Chinese tech company, has been actively exploring the possibilities of RISC-V and contributing to its ecosystem with the Xuantie 910, a powerful 16-core, 2.5 GHz RISC-V processor.

Meanwhile, Western Digital, a leader in data storage solutions, has been evaluating RISC-V for use in storage and memory controllers and published SweRV, an open-source RISC-V core implementation developed in-house to support their transition towards the free and open instruction set architecture. The popularity of GigaDevice's GD32VF103 MCU series and Microchip Technology's adoption of PolarFire-SoCs with RISC-V-based microprocessor subsystems reveal the growing market demand for commercially viable RISC-V products, and Nvidia's involvement in RISC-V for its automotive SoCs emphasizes the architecture's broad impact on various sectors. As RISC-V continues to garner support and adoption, it cements its position as a game-changer in the world of computer architecture.

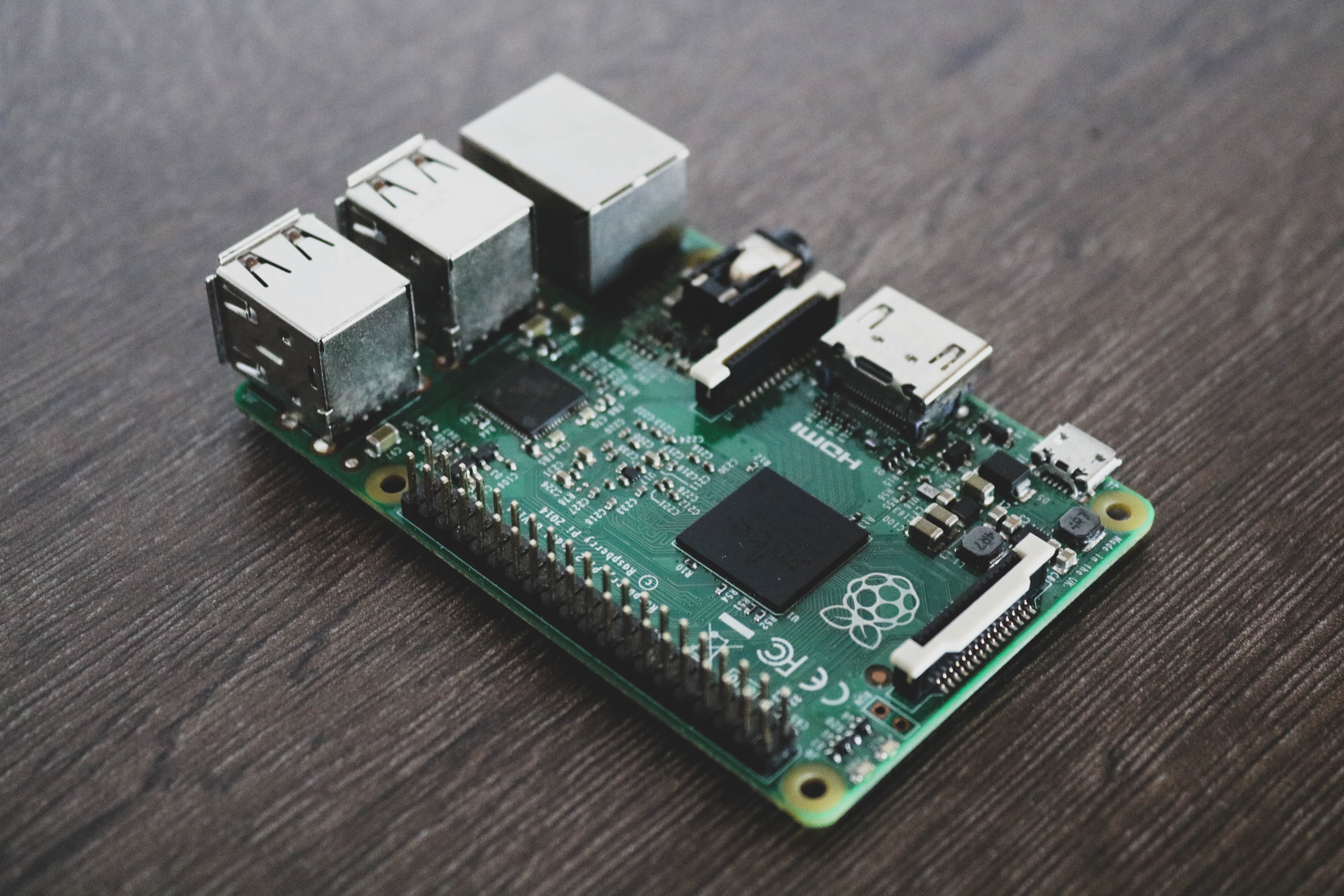

This is a Raspberry Pi 1 Model B+ (2014), which uses the ISA ARM.

What does RISC-V look like?

|

|

What sets RISC-V apart from its competitors?

Firstly, the open-source nature of RISC-V fosters transparency, allowing developers to access and understand the inner workings of the architecture. It promotes flexibility, enabling customization and adaptation to specific requirements and use cases. This openness also encourages a vibrant ecosystem of developers who can freely contribute to the advancement and improvement of the architecture.

Furthermore, RISC-V's modular design allows system designers to optimize performance, power consumption, and features for their specific applications. The flexibility to tailor the processor to specific needs can result in improved efficiency and better utilization of resources. Additionally, RISC-V's reduced instruction set architecture (ISA) simplifies hardware design and facilitates better code optimization. The streamlined instruction set enables developers to write more efficient and compact code, leading to improved performance and energy efficiency. This makes RISC-V particularly well-suited for embedded systems and Internet of Things (IoT) devices.

What advantages does RISC-V have?

Several benefits contribute to RISC-V's growing popularity:

- Cost-Effectiveness: ARM, Intel and AMD are the largest competitors of RISC-V, and they either limit the usage of their architecture for themselves or charge other companies high licensing fees; meanwhile, RISC-V is free-to-use.

- Reduced Vendor Lock-In: With RISC-V being open-source and standardized, it reduces the risk of vendor lock-in that proprietary ISAs often impose. Companies can switch between RISC-V implementations or develop their custom designs without being tied to a specific vendor.

- Transparency and Understanding: Being open-sourced helps developers to examine the architecture's design, logic, and implementation and to get a deeper understanding of the inner workings, thus promoting better code optimization and efficient utilization of resources.

- Customization and Adaptation: Users can modify the RISC-V architecture to suit their specific requirements and use cases. This flexibility enables system designers to optimize performance, power consumption, and features for their applications.

- Collaborative Development: The open-source environment encourages a collaborative community of developers. They can freely contribute to the architecture's improvement and enhancement, benefiting from diverse perspectives and expertise.

- Innovation and Experimentation: With open access to the architecture, innovators can experiment and explore novel approaches, driving continuous innovation and pushing the boundaries of computing.

- Scalability: RISC-V is scalable across a broad spectrum of devices, from microcontrollers to high-performance server processors. Its design flexibility allows it to be used in diverse applications, from embedded systems to data centers.

- Vendor Flexibility: RISC-V's open standard allows companies to work with multiple vendors for chip design and manufacturing, creating a competitive market. This flexibility can lead to more favorable pricing and better negotiation power when selecting partners.

How will RISC-V develop in the future?

Despite being primarily recognized for its x86 processors (one of the competitors of RISC-V), Intel also acknowledges the promising future of RISC-V. Intel Foundry Services is collaborating with IP providers to ensure that RISC-V operates efficiently on their silicon, demonstrating their belief in the potential of this open-source instruction set architecture. With even competitors acknowledging RISC-V's potential as a rising star, the future of RISC-V appears promising and transformative in the world of computer architecture.

Recent advancements have expanded the usability of RISC-V architecture, exemplified by Debian's support for it in the unstable archive since the end of July, with plans for integration in the stable version of the next major Debian release (Debian 13 “Trixie”) or the collaboration of prominent players in the semiconductor industry to drive the advancement of the RISC-V architecture announced at August 4th. This significant development paves the way for broader adoption and usage of RISC-V technology. As more companies actively explore and invest in RISC-V, the ecosystem continues to flourish, driving innovation and collaboration. Additionally, the availability of open-source RISC-V cores and tools fosters a vibrant community, encouraging contributions from developers and enthusiasts worldwide.

With the IoT market rapidly expanding, RISC-V's role in this domain is expected to become even more critical in shaping the future of connected devices and smart technologies. Envision a future where RISC-V powers a transformative revolution in transportation, enabling autonomous vehicles to navigate with ease, while simultaneously empowering our smart fridges to leverage its open-source prowess, autonomously handling grocery restocking. Moreover, RISC-V's versatility might even play a crucial role in the next Mars rover's expedition, making it a trailblazer in interplanetary exploration.

What is the future of this blog?

We hope you found this article on RISC-V insightful and informative, and that it provided you with a deeper understanding of this open-source instruction set architecture and its growing impact across various industries.

As technology enthusiasts, we invite you to stay tuned to this blog for more exciting updates and comparisons between ARM and RISC-V, particularly focusing on performance and energy consumption aspects.

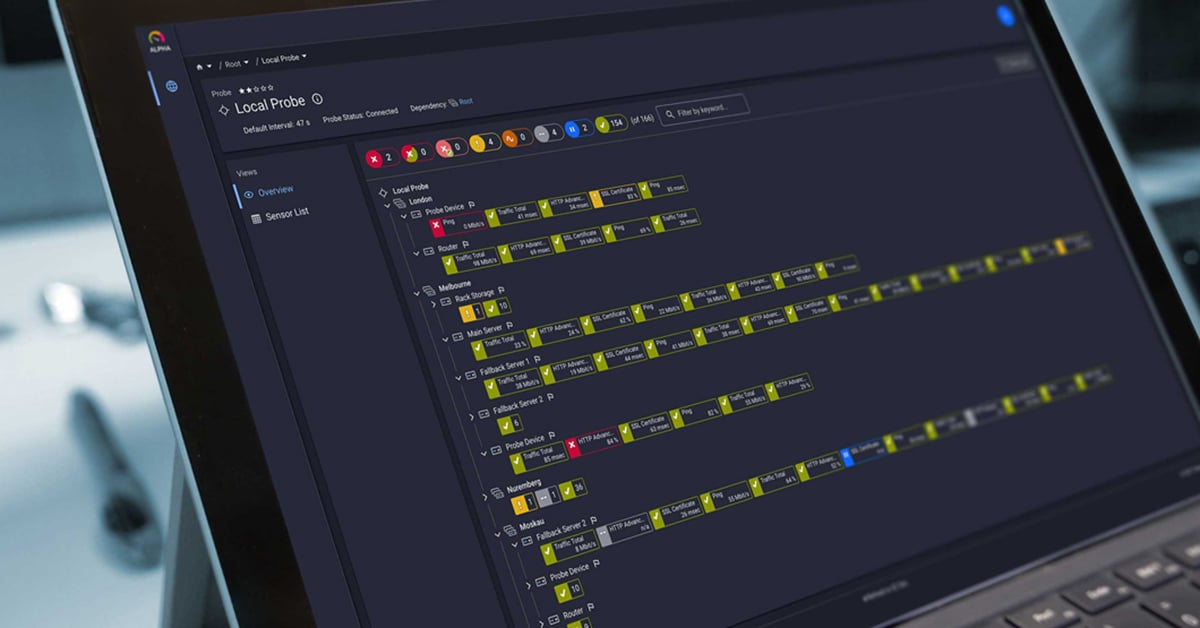

Moreover, we will explore the relevance of RISC-V in the context of Paessler PRTG monitoring software, shedding light on how this innovative architecture contributes to the advancements in monitoring and managing modern computing systems. Join us on this journey as we continue to delve into the world of RISC-V and its fascinating developments in the ever-evolving landscape of computer architecture.

Published by

Published by